探针台

Probe Stations

文章内容参考论文:“O-band low loss and polarization insensitivity bilayer and double-tip edge coupler”

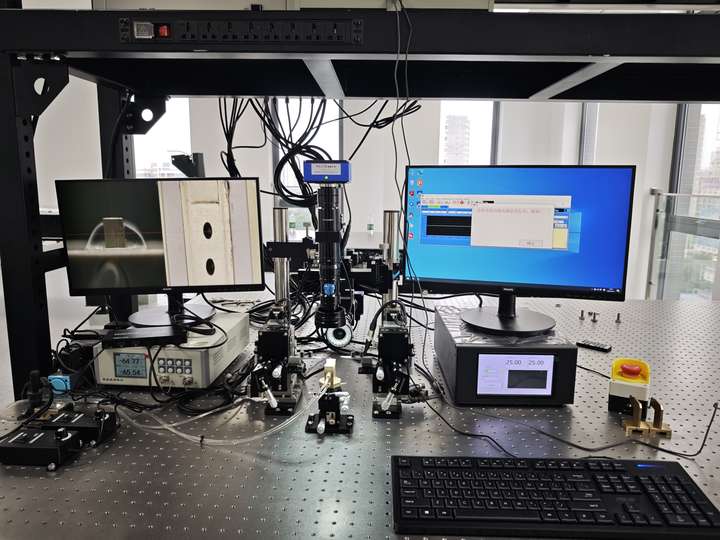

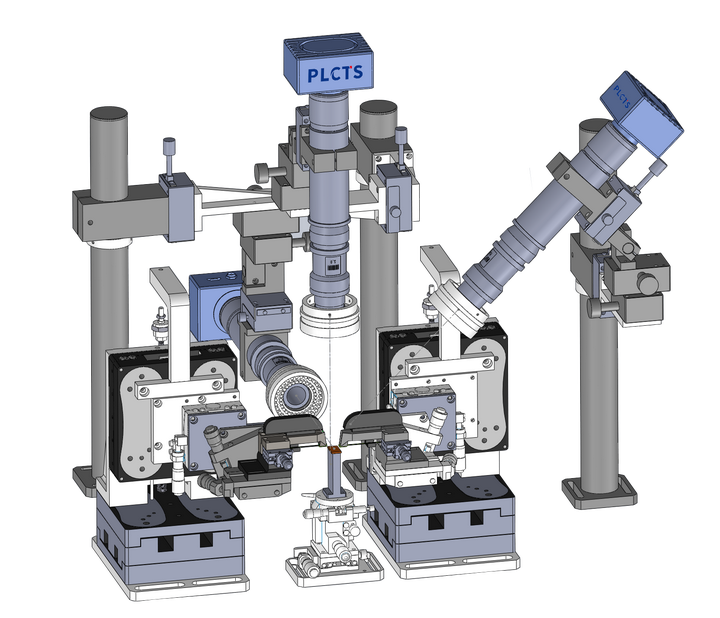

文章使用设备:光纤波导耦合系统

硅基光子集成电路(PIC)作为光通信、计算和传感等领域的核心技术,正推动着高速光互连与集成光子学的飞速发展。然而,硅光子芯片与光纤的高效耦合始终是制约其大规模应用的关键挑战之一。传统端面耦合器在O波段(1260-1360 nm)因硅波导的强双折射特性,面临显著的偏振相关损耗(PDL),导致TE和TM模式的耦合效率差异较大。如何在保持制造工艺兼容性的同时实现低损耗、宽带宽且偏振不敏感的耦合,成为学术界与工业界共同关注的难题。

近日,有教授团队提出了一种双层双尖端端面耦合器,通过创新结构与工艺设计,成功在O波段实现TE/TM双模高效耦合。实验结果表明,TE模式耦合损耗低至1.18 dB/facet,TM模式耦合损耗仅为1.46 dB/facet(1310 nm波长),且在整个O波段内性能稳定,兼容商用硅光工艺。该成果为解决O波段端面耦合器的偏振敏感问题提供了有效方案。研究以“O-Band Low Loss and Polarization Insensitivity Bilayer and Double-tip Edge Coupler”为题。

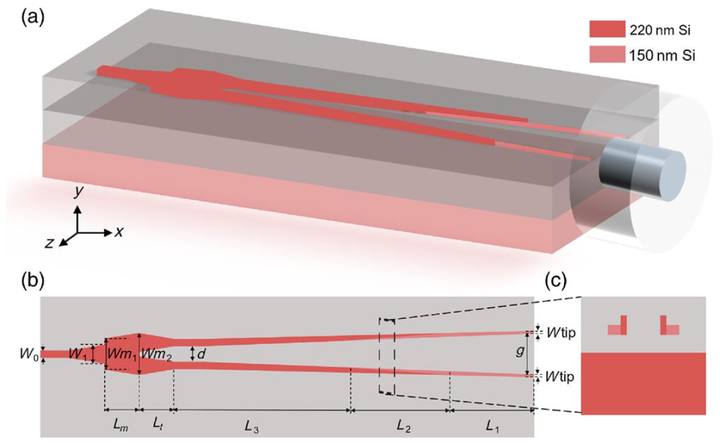

端面耦合器是实现芯片与光纤连接的核心器件,其性能直接取决于波导模场与光纤模场的匹配程度。本文提出的双层双尖端端面耦合器(图1)通过协同优化波导结构与双尖端设计,显著降低了模式场失配与偏振依赖性。本文提出了一种基于双层与双尖端边缘耦合器的创新方案,旨在实现O波段光纤与芯片间的高效耦合,同时最大限度降低偏振态损耗(PDL)。通过采用多重刻蚀工艺,我们有效降低了波导的纵向模式约束,实现了横向电场模(TE)和横向磁场模(TM)的高耦合效率。实验验证表明,该边缘耦合器在整个O波段范围内性能优异,当与具有模式场直径(MFD)4μm的透镜光纤耦合时,两种偏振方向的耦合损耗均低于2 dB/端面。

图1:双层双尖端端面耦合器示意图

图 1:

(a)双层和双头边缘耦合器的示意图。

(b)边缘耦合器的横截面图像。

(c)高度过渡过程的横截面图像。

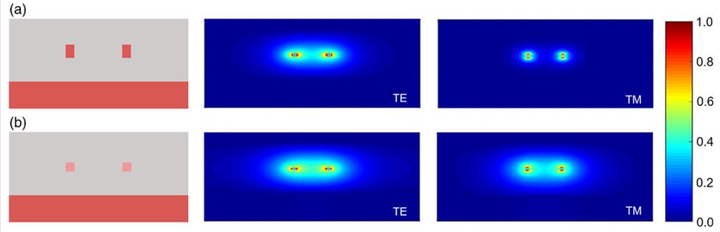

通过仿真分析发现,传统220 nm高度的波导对TM模式的强限制导致其有效模场面积远小于TE模式(图2a)。为此,团队采用另一种常用的150 nm波导高度(图2b),通过降低纵向模式束缚,使TM模场面积大幅提升。其中E₁和E₂分别表示光纤模式与芯片波导模式的复电场振幅。为提升耦合效率,需设计与输入光纤模式高度匹配的波导结构。如图2(a)和2(b)所示,我们通过仿真分析计算了两种不同高度波导结构在1310纳米波长下的TE和TM模式场分布。从图2(a)可见,TE模式的有效模面积明显大于TM模式。这源于1310纳米波长下波导的强双折射特性——220纳米高的波导对TM模式具有更强的约束作用,导致其模尺寸更小。因此我们将波导高度调整为150纳米以降低TM模式的约束效应。如图2(b]仿真结果所示,在此配置下TE和TM模式的有效模面积基本保持一致。

综上,通过仿真分析发现,传统220 nm高度的波导对TM模式的强限制导致其有效模场面积远小于TE模式(图2a)。为此,团队采用另一种常用的150 nm波导高度(图2b),通过降低纵向模式束缚,使TM模场面积大幅提升。

图2:双头波导以及TE和TM模式场分布的横截面图像

图2:双头波导以及TE和TM模式场分布的横截面图像。

(a) 220 nm 高。

(b) 150 nm 高。

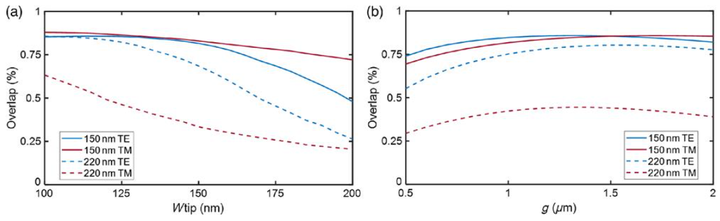

为定量分析两种波导结构的差异并实现更高耦合效率,我们针对尖端波导宽度和间距进行了优化设计,并计算了其与4μm MFD透镜光纤模式的重叠度。首先,我们对尖端波导宽度进行了优化模拟(如图3(a)所示)。图中实线和虚线分别代表高度为150纳米和220纳米的波导结构,红色和蓝色线条分别对应TE和TM模式。从仿真结果可见,红色实线的整体重叠度比红色虚线高出20%以上,充分证明了我们设计方法的有效性。当波导结构高度为220纳米时,TE和TM模式的重叠度存在显著差距,难以同时实现高效耦合与光子带隙(PDL)的双重目标。然而,当波导结构高度为150纳米时,在100至150纳米的尖端宽度范围内,两种模式的重叠度均接近80%以上。

图3:220 nm和150 nm 高度下不同偏振耦合效率分析

图3:计算的模式重叠度随(a)Wtip和(b)g的变化关系

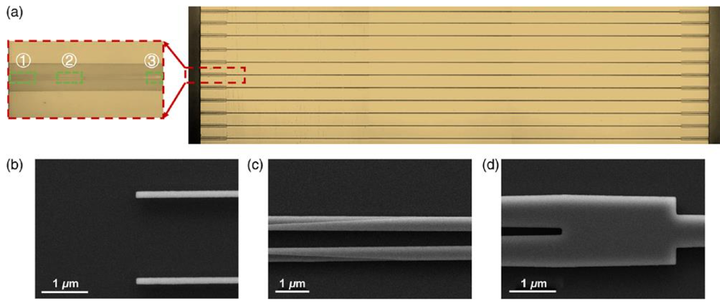

团队设计的器件是在SOI晶圆上制造的,其顶部硅层厚度为220纳米,埋入式二氧化硅层厚度为2μm。该器件设计分为两层结构,通过多道蚀刻工艺完成。首先使用电子束光刻(EBL)技术,在晶圆表面旋涂ZEP520电子束抗蚀剂。随后利用EBL将图案转印至抗蚀剂层。接着通过电子束蒸发沉积10/50纳米厚的铬/金金属层,并进行剥离处理去除多余金属,最终形成图案化结构。在第二步EBL工艺中,将第一层结构转印至电子束抗蚀剂层。为将结构转印至硅层,采用电感耦合等离子体(ICP)蚀刻工艺对顶部硅层进行220纳米深度蚀刻。在另一轮EBL和ICP工艺中,将第二层结构转印至硅层并蚀刻70纳米。最后通过等离子体增强化学气相沉积法在顶部沉积2μm厚的二氧化硅包覆层。图6(a)展示了器件的光学显微镜图像,插图为边缘耦合器的放大视图。图6(b)-6(d)为图6(a]插图中标记区域的扫描电子显微镜(SEM)图像。

团队采用电子束曝光(EBL)与感应耦合等离子体(ICP)刻蚀等技术,通过两次EBL步骤分别定义双层结构。第一层刻蚀深度为220 nm,第二层刻蚀70 nm,最终形成150 nm高度的双尖端波导(图4b-d)。通过精确控制刻蚀参数,团队实现了纳米级精度的波导形貌,并利用等离子体增强化学气相沉积(PECVD)技术沉积2 μm厚的SiO₂包层,确保器件长期稳定性。

图4:端面耦合器显微图

图4:

(a)单芯片切割后的光学显微镜图像。

(b)-(d)制备的边缘耦合器的扫描电镜图像。

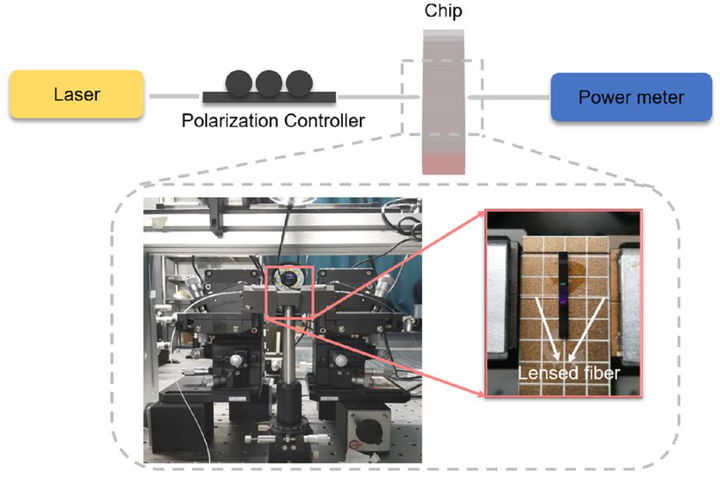

为表征所制备的边缘耦合器性能,我们采用波长范围在1260至1360纳米之间的可调谐激光器作为输入光源。通过光功率计测量芯片输出端的耦合功率,并使用偏振控制器将输入光的偏振态控制在TE和TM模式之间。耦合装置 该装置由两个精密六轴对准台、2个观察系统(垂直+水平)和一个芯片支架组成,如图7插图所示。我们在光纤支架两侧各固定一根4-MM MFD透镜光纤,并通过调整六轴对准台使功率计测得的光功率最大化。通过调节输入光波长和偏振控制器,我们对器件在整个0波段范围内的TE和TM耦合损耗进行了表征。图8展示了器件的测试与仿真性能对比,其中实线和虚线分别代表实验与仿真结果,红色和蓝色曲线分别对应TE和TM模式数据。观察发现实验结果虽略逊于仿真结果,但两者呈现一致趋势,充分展现了器件在偏振相关损耗方面的卓越性能。在1310 nm波长下,TE和TM模式耦合损耗分别测量为1.18 dB/端面和1.46 dB/端面。光谱中出现的噪声源于测试过程中耦合装置的振荡以及光纤与芯片间的反射。在整个0波段范围内,TE和TM模式耦合损耗分别<1.52 dB/端面和2 dB/端面。

图5:波导耦合系统

该端面耦合器在O波段的高效表现,使其成为高速数据通信(如5G和下一代数据中心)中光纤-芯片接口的理想解决方案。其低偏振敏感特性尤其适用于偏振复用系统,可显著降低系统复杂度与成本。随着O波段在短距通信和传感领域的广泛应用,此类高性能耦合器有望成为下一代光子集成芯片的核心组件,推动光电子产业持续革新。